# AN1432: SiWx917 NCP SPI Protocol Application Note

Version 1.0 May 2024

silabs.com | Building a more connected world.

# **Table of Contents**

| 1 | Introduction                                                  | 3  |

|---|---------------------------------------------------------------|----|

|   | 1.1 SPI Features                                              | 3  |

| 2 | Prerequisites                                                 | 4  |

| 3 | Terminology                                                   | 5  |

| 4 | SiWN917 SPI App Note for Hardware and Software Configurations | 6  |

|   | 4.1 Description                                               | 6  |

|   | 4.2 SPI Modes                                                 | 7  |

|   | 4.3 SPI Transactions Logic Capture                            | 8  |

|   | 4.4 SiWN917 SPI Logs Decoding Guide                           | 10 |

|   | 4.5 Recommendations Based on Software Configurations          | 16 |

| 5 | Summary                                                       | 18 |

## 1 Introduction

This document provides information on the hardware design and software configurations for the host SPI interface available in SiWx917 NCP or hereby termed as SiWN917.

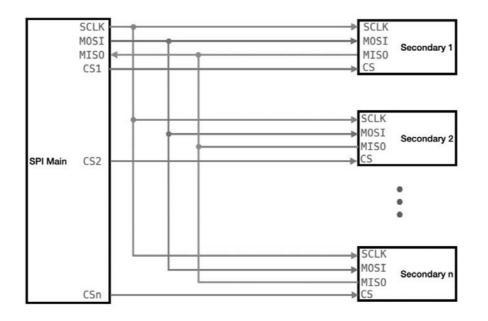

Serial Peripheral Interface (SPI) is one of the most widely used serial interfaces between microcontrollers and peripheral ICs, such as sensors, ADCs, DACs, Shift Registers, SRAM, and others including modems. Every SPI system consists of one primary/main device and one or more secondary devices, where the main device initiates the communication by asserting the CSn (nth Chip Select) line. When a secondary device is selected, the primary starts clocking out the data through the MOSI (Main Out Secondary In) line and receives the data through the MISO (Main In Secondary Out) line. The primary sends and receives one bit for every clock edge. One byte can be exchanged in eight clock cycles. The main device finishes communication by de-asserting the CSn line.

#### 1.1 SPI Features

Some of the notable features of SPI protocol are:

- Full-duplex communication in the default version of this protocol.

- • Push-pull (as opposed to open-drain) provides good signal integrity and high speeds.

- Higher throughput than I2C or SMBus. Not limited to any maximum clock speed, enabling potentially high speeds for data transfer.

- Complete protocol flexibility for the bits transferred.

- Extremely simple hardware interfacing.

- Uses only four pins on IC packages and wires in board layouts or connectors, fewer than in parallel interfaces.

- At most, one unique bus signal per device (chip select); all others are shared.

- Signals are unidirectional allowing for easy galvanic isolation.

- Simple software implementation.

- SPI Secondary Interface supports 8-bit and 32-bit data granularity.

- It also supports the gated mode of SPI clock, and the Low, High and Ultra high-frequency modes.

## 2 **Prerequisites**

- Windows PC with host interface (USB/UART/SPI/SDIO).

- MCU/Host with SPI-main interface (e.g. EFR32).

- Any logic analyzer for analyzing the data lines.

- IDE to create an application for the host (e.g. Simplicity Studio).

- BRD8045A EXP Adapter Board for <u>SiWx917</u> Co-processors.

## 3 Terminology

- SPI Serial Peripheral Interface

- MOSI Main Out Secondary In

- MISO Main In Secondary Out

- CSN Chip Select Bar

- PC Personal Computer

- IDE Integrated Development Environment

## 4 SiWN917 SPI App Note for Hardware and Software Configurations

### 4.1 Description

SiWx917 NCP mode (SiWN917) supports only the SPI secondary interface. SiWN917 detects the host interface automatically after connecting to respective host controllers like SDIO, SPI, UART, USB and USB-CDC. SPI interfaces are detected through hardware packet exchanges. Below are the signal descriptions for the SPI interface. For more details about the pin names and descriptions, please refer to the <u>SiWx917</u> datasheet.

| Signal Name  | Supply Domain | Direction | Initial State                                 | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|--------------|---------------|-----------|-----------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|              |               |           | (Power-up, Active<br>Reset & Sleep State)     | (All signals are in default states unless otherwise mentioned)                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| SPI_CLK      | SDIO_IO_VDD   | Input     | High-Z                                        | Serial Clock Input                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| SPI_CSN      | SDIO_IO_VDD   | Input     | High-Z                                        | Active-low Chip Select signal initiated<br>by the main device to select a<br>secondary device                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| SPI_MOSI     | SDIO_IO_VDD   | Input     | High-Z                                        | Main-Out-Secondary-In signal for data transfer from main device to secondary device                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| SPI_MISO     | SDIO_IO_VDD   | Output    | High-Z                                        | Main-In-Secondary-Out signal for data transfer from Secondary to main device                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| SPI_INTR     | SDIO_IO_VDD   | Output    | High-Z                                        | Interrupt signal to main device for<br>indicating that the data is available with<br>the Secondary device. Upon interrupt,<br>main device must initiate SPI<br>transaction and read the available data<br>on the SPI_MISO line. For more details<br>about this signal, read the below 'Note'<br>section.                                                                                                                                                                                                                      |

| SPI_ERR_INTR | SDIO_IO_VDD   | Output    | Initial State: Pull-up<br>Sleep State: High-Z | This signal is not available in the<br>Default state. Check its availability in<br>the Software. If SPI core logic within<br>the device has gone to a state where it<br>is not able to recover and process SPI<br>transactions from the external main<br>device, then SPI_ERR_INTR is<br>asserted to the external main device<br>about this status. It is an active high<br>output signal. Once this signal is<br>asserted by the devices, then the<br>external host must initialize SPI and<br>start the transactions again. |

#### NOTE

- "Default" state refers to the state of the device after initial boot loading and firmware loading is complete.

- "Sleep" state refers to the state of the device after entering Sleep state which is indicated by Active-High 'SLEEP\_IND\_FROM\_DEV' signal.

- Refer to the <u>WiSeConnect API Reference Guide</u> for software programming information in embedded mode.

Ensure that the input signals, SPI\_CSN, and SPI\_CLK are not floating when the device is powered up and reset is deasserted. This can be done by ensuring that the host processor configures its signals (outputs) before de-asserting the reset. '**SPI\_INTR**' is the interrupt signal driven by the secondary device. This signal may be configured as Activehigh or Active-low. If it is active-high, an external pull-down resistor may be required. If it is active-low, an external pull-up resistor may be required. This resistor can be avoided if the following action needs to be carried out in the host processor.

- 1. To use the signal in active-high or active-low mode, ensure that during the power-up of the device the interrupt is disabled in the host processor before de-asserting the reset. After de-asserting the reset, the interrupt needs to be enabled only after the SPI initialization is done, and the interrupt mode is programmed to either active-high or active-low mode as required.

- 2. The host processor needs to disable the interrupt before the ULP Sleep mode is entered and enable it after the SPI interface is reinitialized upon wakeup from ULP Sleep.

#### 4.2 SPI Modes

There are four SPI modes, as shown in the below table.

| SPI Mode | Clock Polarity<br>(CPOL) | Clock Phase<br>(CPHA) | Source                                      | Destination                                  |

|----------|--------------------------|-----------------------|---------------------------------------------|----------------------------------------------|

| 0        | 0                        | 0                     | Data driven on rising edge<br>of the clock  | Data sampled on falling edge<br>of the clock |

| 1        | 0                        | 1                     | Data driven on falling edge<br>of the clock | Data sampled on rising edge<br>of the clock  |

| 2        | 1                        | 0                     | Data driven on falling edge<br>of the clock | Data sampled on rising edge<br>of the clock  |

| 3        | 1                        | 1                     | Data driven on rising edge<br>of the clock  | Data sampled on falling edge<br>of the clock |

**NOTE:** SiWN917 supports only Mode-0 and Mode-3 from the above. As of now, SiWN917 is brought up in Mode-0 by default, and there is no API available for changing the mode.

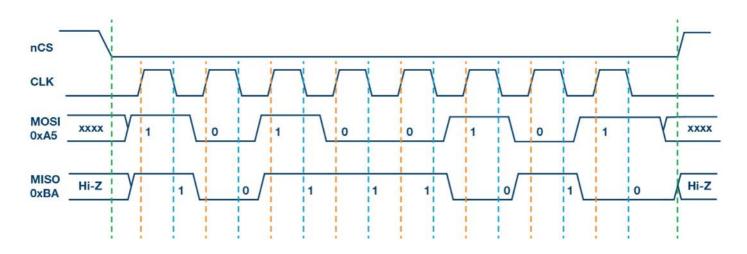

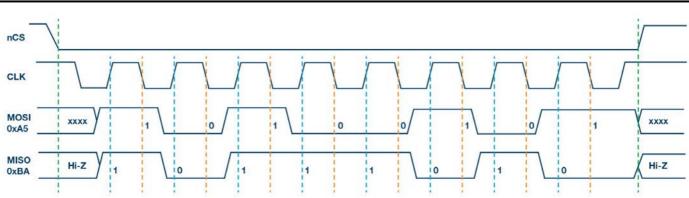

The following are the example diagrams for Mode-0 and Mode-3 respectively. The data is shown on the MOSI and MISO lines. The start and end of transmission are indicated by the dotted green line. The dotted orange line indicates the data-driven by the source, and the dotted blue line indicates the data sampled by the destination.

In Mode-0, clock polarity is '0' which indicates that the idle state of the clock signal is low. The clock phase in this mode is '0'. Data transmission occurs during the rising edge of the clock.

In Mode-3, the clock polarity is '1' which indicates the idle state of the clock signal is high. The clock phase in this mode is 1. Data transmission occurs during the rising edge of the clock.

#### 4.3 SPI Transactions Logic Capture

LABS

SILICON

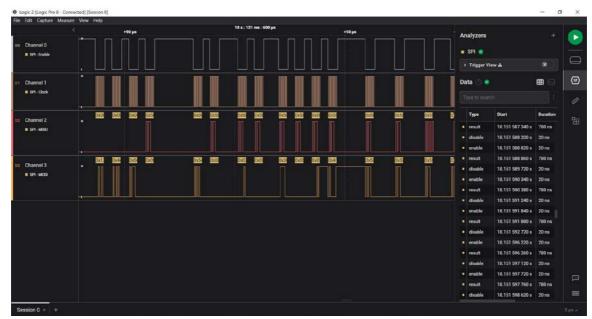

In this section, SPI transactions between SiWN917 and EFR32xG21 MCU are captured using <u>Logic Software</u>. The following are the setup instructions for SPI protocol in 'Logic software'.

- Connect the Saleae Logic analyzer pins with the SPI pins on the host MCU for SPI logic capture.

- Open the 'Logic' software and click on the 'Device Settings' tab towards the right side of the Logic software screen and select the 'Digital 'channels that are connected with Saleae Logic Analyzer.

- Select the sampling rate. This must be greater than the SPI clock frequency being used by host MCU for communication with SiWN917 (Generally, the higher the better).

| Logic 2 [Logic Pro 8 - Conn |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                               |                        |                   | – a × |

|-----------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------|------------------------|-------------------|-------|

| File Edit Capture Measure   | e View Help<br>< *18 s:151 ms:500 µs<br>+90 µs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 18 s : 151 ms : 600 µs<br>+10 |                        |                   |       |

| po Channel 0                | The net of the second sec |                               | Logic Pro 8<br>Digital |                   |       |

| SP1 - Enable                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                               | 0 1 2 3 4 5            |                   |       |

| 01 Channel 1                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                               | 50 MS/s v 1.2 Volts    |                   | æ     |

| SPI-Clock                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                               | Analog<br>0 1 2 3 4 5  |                   |       |

| 92 Channel 2<br>SPI-MSD     | (20x00 0x00 0x00 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                               |                        |                   |       |

| D3 Channel 3<br>SPI-MOSI    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                               | Looping Timer          | Trigger<br>8<br>8 |       |

|                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                               | Memory buffer size     |                   |       |

|                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                               | - 3 CB                 | +                 |       |

|                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                               |                        |                   |       |

|                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                               |                        |                   |       |

|                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                               |                        |                   | =     |

| Session 0 × +               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                               |                        |                   |       |

- Now click on 'Analyzers' tab towards the right side of the screen and select 'SPI'.

- A new 'SPI' window is opened. Select the corresponding channels for SPI MOSI, MISO, Clock and Enable.

Select 'Most Significant Bit First' as the significant bit, clock state as CPOL = 0 and clock phase as CPHA = 0.

Other settings must be made as per the below image.

| SPI 💿             |                                                | ×    |

|-------------------|------------------------------------------------|------|

| MOSI              | 03. Channel 3                                  |      |

| MISO              | 02. Channel 2                                  |      |

| Clock *           | 01. Channel 1                                  |      |

| Enable            | 00. Channel O                                  |      |

| Significant Bit   | Most Significant Bit First (Standard)          |      |

| Bits per Transfer | 8 Bits per Transfer (Standard)                 |      |

| Clock State       | Clock is Low when inactive (CPOL = 0)          |      |

| Clock Phase       | Data is Valid on Clock Leading Edge (CPHA = 0) |      |

| Enable Line       | Enable line is Active Low (Standard)           |      |

|                   | Show in protocol results table                 |      |

|                   | Stream to terminal                             |      |

| Reset             | Cancel                                         | Save |

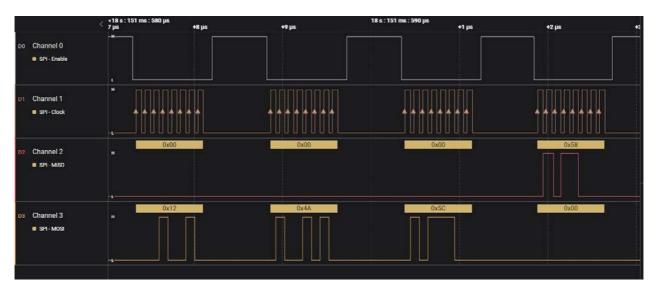

Once the above setup is complete, one should see the SPI transactions in the 'Logic Software' as soon as an SiWx917 Wi-Fi/BLE application is run and the 'Play' button is clicked in Logic software. These transactions should look like the following:

#### NOTE

- To be precise, the above SPI transactions can be captured when "sl\_net\_init()" API (defined in the 'wiseconnect/components/service/network\_manager' sub-component of the <u>WiSeConnect SDK</u> is run. Driver initialization, device initialization, and wireless initialization happen within this API. As an out-of-box experience, users can run any default WiSeConnect example from the SDK folder, 'wiseconnect/examples/featured' or 'wiseconnect/examples/snippets' where this API is called in the corresponding 'app.c' file of the application.

- Before running an application, users must ensure they successfully port the WiSeConnect SDK HAL (Hardware Abstraction Layer) to the host MCU in use. For more information on HAL porting, refer to 'SiWx91x NCP WiSeConnect 3 SDK Porting Guide'. The SDK is already ported to EFx32 family of MCUs and the corresponding HAL can be found in 'wiseconnect/components/si91x/platforms/efx32'.

With EFx32 as the host MCU, the host SPI interface is brought-up with 12.5 MHz SPI clock frequency (Check the baud rate in the definition of 'sl\_si91x\_host\_usart2\_init()' API present in the file, 'wiseconnect/components/si91x/platforms/efx32/efx32\_ncp\_host\_spi.c'). To enable high-speed mode, the user has to implement the 'sl\_si91x\_host\_enable\_high\_speed\_bus()' API for the host MCU in use as part of the HAL porting. For EFx32, this has been implemented (definition can be found in 'efx32\_ncp\_host\_spi.c' file). Note that SiWx917 host SPI interface supports host SPI clock frequencies up to 100 MHz.

#### 4.4 SiWN917 SPI Logs Decoding Guide

The SPI transaction flow between SiWN917 and the host MCU is described in this section. The following are captures of the SPI transfers after a module hardware reset.

#### **SPI** Initialization

The SPI initialization process takes place during 'device initialization'. The host MCU needs to initialize SPI to communicate with SiWN917. This is done by transmitting 0x12, 0x4A, 0x5C, 0x00 on the MOSI line. After successful SPI initialization, SiWN917 sends a success token, i.e., 0x58 on MISO line.

#### MOSI: 0x12 0x4A 0x5C 0x00

MISO: 0x00 0x00 0x00 0x58 (Successful SPI Initialization)

**NOTE:** If your application requires SPI clock frequency greater than 25 MHz, the host must initialize the SPI interface with a clock frequency less than or equal to 25 MHz. Post SPI initialization, all the other SPI transactions can be carried out at a clock frequency greater than 25 MHz. This functionality is to be implemented while porting WiSeConnect 3 SDK to your host application. Refer to <u>Porting for an External Host</u> guide.

Before going further, it is necessary to note the following SPI tokens sent by SiWN917 over MISO:

- **0x58** Success response

- 0x52 Failure response

- **0x54** Busy response (a new transaction is initiated while the previous transaction's response is still pending from the module)

- **0x55** Start token (Module is ready to transmit data)

#### NOTE:

- Recommendation: Use a SPI cable of less than 2 inches length for prototyping.

- If the SPI cable is not connected properly between the host and SiWN917, the host MCU waits for the response from the module for some reasonable time and throws 'SL\_STATUS\_SPI\_BUSY' error (with error code: 0x0054) for device initialization.

#### SPI Transactions For 'BOARD READY' And 'CARD READY' Messages

**BOARD READY:** After successful initialization of the SPI interface with the module, the first message checked by the host is **'BOARD READY'** from the module. If the bootup options integrity passes, the **RSI\_HOST\_INTF\_REG\_OUT** register contains **0xABxx** where 'xx' represents the two-nibble bootloader version.

**CARD READY:** After the firmware gets loaded onto the module successfully, **'CARD READY'** is the first message from the loaded firmware that is sent to the Host MCU.

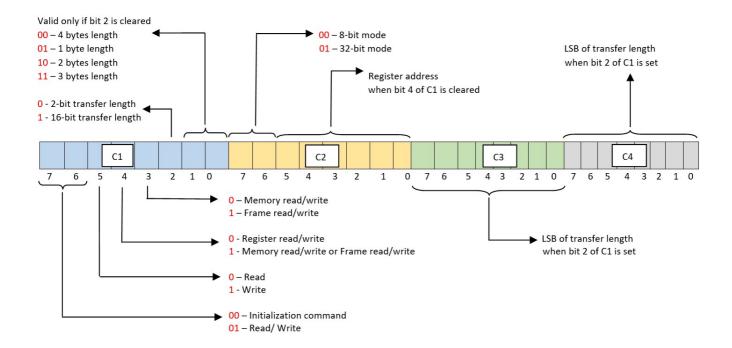

The SPI interface is programmed to perform transfers using commands C1, C2, C3 and C4 and an optional 32-bit address (sent during register read/write or memory read/write).

After successful initialization of the SPI interface, the host waits for **'BOARD READY'** from the module. For checking the **BOARD READY** from the module, the host reads the contents of **RSI\_HOST\_INTF\_REG\_OUT** register of module with LSB of address transmitted first.

| MOSI Byte Explained<br>(Tx to Module)                   | MOSI | MISO | MISO Byte<br>Explained<br>(Tx to Host MCU) | Other Possibilities |

|---------------------------------------------------------|------|------|--------------------------------------------|---------------------|

| Memory Read                                             | 0x54 | 0x00 | Dummy data                                 | -                   |

| 8-bit Mode                                              | 0x00 | 0x58 | Success token                              | 0x52, 0x54          |

| LSB of the length of data to be read - Two bytes        | 0x02 | 0x58 | Success token                              | 0x52, 0x54          |

| MSB of the length of data to be read                    | 0x00 | 0x58 | Success token                              | 0x52, 0x54          |

| RSI_HOST_INTF_REG_OUT<br>Address to be read (LSB first) | 0x3C | 0x58 | Success token for<br>Memory Read           | 0x52, 0x54          |

|                                                         | 0x00 | 0x58 | Success token                              | 0x52, 0x54          |

|                                                         | 0x05 | 0x58 | Success token                              | 0x52, 0x54          |

|            | 0x41 | 0x58 | Success token                                                                                                                                                         | 0x52, 0x54                                                                                                                                           |

|------------|------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------|

| Dummy data | 0x00 | 0x58 | Success token                                                                                                                                                         | 0x52, 0x54                                                                                                                                           |

| Dummy data | 0x00 | 0x55 | Start token followed by two bytes of data                                                                                                                             | 0x52, 0x54                                                                                                                                           |

| Dummy data | 0x00 | 0x11 | Bootloader version<br>1.1                                                                                                                                             | 0x10 – Bootloader version 1.0                                                                                                                        |

| Dummy data | 0x00 | 0xAB | HOST_INTERFACE_<br>REG_OUT_VALID<br>(0xAB11 or 0xAB10<br>indicates that the<br>bootloader integrity<br>check is passed. This<br>is named as 'BOARD<br>READY' message) | 0xABF1 – indicates that the last<br>configuration of bootup options is not<br>saved<br>0xABF2 – indicates that the bootup<br>options checksum failed |

Before checking the **CARD READY** from the module, the host needs to check whether the Interrupt signals are active low or active high. This can be known from the contents of **'RSI\_INT\_MASK\_REG\_ADDR'** register (at address 0x41050000) of module by performing memory read to that address.

| MOSI Byte Explained                                     | MOSI | MISO | MISO Byte Explained                       | Other         |  |

|---------------------------------------------------------|------|------|-------------------------------------------|---------------|--|

| (Tx to Module)                                          |      |      | (Tx to Host MCU)                          | Possibilities |  |

| Memory Read                                             | 0x54 | 0x00 | Dummy data                                | -             |  |

| 8-bit Mode                                              | 0x00 | 0x58 | Success token                             | 0x52, 0x54    |  |

| LSB of the length of data to be read<br>- Two bytes     | 0x02 | 0x58 | Success token                             | 0x52, 0x54    |  |

| MSB of the length of data to be read                    | 0x00 | 0x58 | Success token                             | 0x52, 0x54    |  |

| RSI_INT_MASK_REG_ADDR<br>Address to be read (LSB first) | 0x00 | 0x58 | Success token for Memory Read             | 0x52, 0x54    |  |

|                                                         | 0x00 | 0x58 | Success token                             | 0x52, 0x54    |  |

|                                                         | 0x05 | 0x58 | Success token                             | 0x52, 0x54    |  |

|                                                         | 0x41 | 0x58 | Success token                             | 0x52, 0x54    |  |

| Dummy data                                              | 0x00 | 0x58 | Success token                             | 0x52, 0x54    |  |

| Dummy data                                              | 0x00 | 0x55 | Start token followed by two bytes of data | 0x52, 0x54    |  |

| Dummy data                                              | 0x00 | 0x00 | LSB of the Register                       | 0x52, 0x54    |  |

| Dummy data                                              | 0x00 | 0x01 | MSB of the Register                       | 0x52, 0x54    |  |

|                                                         |      |      | (0x02 – Active Low Interrupts)            |               |  |

For ACTIVE HIGH INTERRUPTS, write '0x00' into RSI\_INT\_MASK\_REG\_ADDR (at address 0x41050000) register of the module.

| MOSI Byte Explained<br>(Tx to Module)                            | MOSI | MISO | MISO Byte Explained<br>(Tx to Host MCU) | Other Possibilities |

|------------------------------------------------------------------|------|------|-----------------------------------------|---------------------|

| Memory Write                                                     | 0x74 | 0x00 | Dummy data                              | -                   |

| 8-bit Mode                                                       | 0x00 | 0x58 | Success token                           | 0x52, 0x54          |

| LSB of the size of the memory<br>into which data must be written | 0x02 | 0x58 | Success token                           | 0x52, 0x54          |

| – Two bytes                                                   |      |      |                                              |                                                                                   |

|---------------------------------------------------------------|------|------|----------------------------------------------|-----------------------------------------------------------------------------------|

| MSB of the size of the memory into which data must be written | 0x00 | 0x58 | Success token                                | 0x52, 0x54                                                                        |

| RSI_INT_MASK_REG_ADDR<br>Address (LSB first)                  | 0x00 | 0x58 | Success token for<br>Memory write<br>command | 0x52, 0x54                                                                        |

|                                                               | 0x00 | 0x58 | Success token                                | 0x52, 0x54                                                                        |

|                                                               | 0x05 | 0x58 | Success token                                | 0x52, 0x54                                                                        |

|                                                               | 0x41 | 0x58 | Success token                                | 0x52, 0x54                                                                        |

| LSB to be written                                             | 0x00 | 0x58 | Success token                                | 0x52, 0x54                                                                        |

| MSB to be written<br>(0x00 – Active High Interrupts)          | 0x00 | 0x58 | Success token                                | MSB = 0x02 – when opted for Active<br>low interrupts during device initialization |

Write **'LOAD FIRMWARE'** instruction into **RSI\_HOST\_INTF\_REG\_OUT** register (at address 0x4105003C) and 'RSI\_HOST\_INTF\_REG\_IN' register (at address 0x41050034) of the module.

| MOSI Byte Explained                                                             | MOSI | MISO | MISO Byte Explained                    | Other Possibilities                                                                  |

|---------------------------------------------------------------------------------|------|------|----------------------------------------|--------------------------------------------------------------------------------------|

| (Tx to Module)                                                                  |      |      | (Tx to Host MCU)                       |                                                                                      |

| Memory Write                                                                    | 0x74 | 0x00 | Dummy data                             | -                                                                                    |

| 8-bit Mode                                                                      | 0x00 | 0x58 | Success token                          | 0x52, 0x54                                                                           |

| LSB of the size of the memory into<br>which data must be written – Two<br>bytes | 0x02 | 0x58 | Success token                          | 0x52, 0x54                                                                           |

| MSB of the size of the memory into which data must be written                   | 0x00 | 0x58 | Success token                          | 0x52, 0x54                                                                           |

| RSI_HOST_INTF_REG_OUT<br>Address (LSB first)                                    | 0x3C | 0x58 | Success token for Memory write command | 0x52, 0x54                                                                           |

|                                                                                 | 0x00 | 0x58 | Success token                          | 0x52, 0x54                                                                           |

|                                                                                 | 0x05 | 0x58 | Success token                          | 0x52, 0x54                                                                           |

|                                                                                 | 0x41 | 0x58 | Success token                          | 0x52, 0x54                                                                           |

| LSB to be written                                                               | 0x00 | 0x58 | Success token                          | 0x52, 0x54                                                                           |

| MSB to be written<br>(Write '0' into<br>RSI_HOST_INTF_REG_OUT<br>Register)      | 0x00 | 0x58 | Success token                          | MSB = 0x02 – when opted<br>for Active low interrupts<br>during device initialization |

| Memory Write                                                                    | 0x74 | 0x00 | Dummy data                             | -                                                                                    |

| 8-bit Mode                                                                      | 0x00 | 0x58 | Success token                          | 0x52, 0x54                                                                           |

| LSB of the size of the memory into<br>which data must be written – Two<br>bytes | 0x02 | 0x58 | Success token                          | 0x52, 0x54                                                                           |

| MSB of the size of the memory into which data must be written                   | 0x00 | 0x58 | Success token                          | 0x52, 0x54                                                                           |

| RSI_HOST_INTF_REG_IN Address<br>(LSB first)                                     | 0x34 | 0x58 | Success token for Memory write command | 0x52, 0x54                                                                           |

|                                                                                 | 0x00 | 0x58 | Success token                          | 0x52, 0x54                                                                           |

|                                                                                 | 0x05 | 0x58 | Success token                          | 0x52, 0x54                                                                           |

|                                                                             | 0x41 | 0x58 | Success token                       | 0x52, 0x54                                                                       |

|-----------------------------------------------------------------------------|------|------|-------------------------------------|----------------------------------------------------------------------------------|

| LSB to be written<br>(Load default firmware with ACTIVE<br>HIGH interrupts) | 0x31 | 0x00 | Dummy data                          | 0x71 – Load default<br>firmware with ACTIVE<br>LOW interrupts                    |

| MSB to be written                                                           | 0xAB | 0x00 | Dummy data                          |                                                                                  |

| (RSI_HOST_INTERACT_REG_OUT<br>Register)                                     |      |      |                                     |                                                                                  |

| Memory Read                                                                 | 0x54 | 0x58 | Success token for memory write      | 0x52, 0x54                                                                       |

| 8-bit Mode                                                                  | 0x00 | 0x58 | Success token                       | 0x52, 0x54                                                                       |

| LSB of the length of data to be read<br>- Two bytes                         | 0x02 | 0x58 | Success token                       | 0x52, 0x54                                                                       |

| MSB of the length of data to be read                                        | 0x00 | 0x58 | Success token                       | 0x52, 0x54                                                                       |

| RSI_HOST_INTF_REG_OUT<br>Address (LSB first)                                | 0x3C | 0x58 | Success token                       | 0x52, 0x54                                                                       |

|                                                                             | 0x00 | 0x58 | Success token                       | 0x52, 0x54                                                                       |

|                                                                             | 0x05 | 0x58 | Success token                       | 0x52, 0x54                                                                       |

|                                                                             | 0x41 | 0x58 | Success token                       | 0x52, 0x54                                                                       |

| Dummy data                                                                  | 0x00 | 0x58 | Success token                       | 0x52, 0x54                                                                       |

| Dummy data                                                                  | 0x00 | 0x55 | Start token                         | 0x52, 0x54                                                                       |

| Dummy data                                                                  | 0x00 | 0xAA | RSI_CHECKSUM_SUCCESS                | 0x23 – When valid<br>firmware is not present and<br>device initialization fails. |

| Dummy data                                                                  | 0x00 | 0xAB | RSI_HOST_INTERACT_REG_<br>OUT_VALID | 0x52, 0x54                                                                       |

• For more information on the boot results, refer to the header file, 'components/si91x/inc/sl\_si91x\_constants.h'.

## Enabling high speed SPI

SPI transfers with clock frequencies up to 25 MHz are termed low-speed transmissions, and during these transmissions, data is driven on the falling edge of the clock and sampled on the rising edge of the clock. Transmissions above 25 MHz are termed high-speed transmissions, and during these transmissions, data is driven on the rising edge of the clock and sampled on the falling edge of the clock. SiWN917 SPI interface also supports Ultra High-Speed mode, with clock frequencies reaching up to 100 MHz. SPI initialization is done in low-speed mode. After initialization, to enable high-speed mode, the following SPI transactions take place:

| MOSI Byte Explained<br>(Tx to Module)    | MOSI | MISO | MISO Byte Explained<br>(Tx to Host MCU) | Other Possibilities                       |

|------------------------------------------|------|------|-----------------------------------------|-------------------------------------------|

| Register Write                           | 0x62 | 0x00 | Dummy data                              |                                           |

| SPI Register's address                   | 0x08 | 0x58 | Success token                           |                                           |

|                                          | 0x00 | 0x58 | Success token                           | 0x52, 0x54                                |

| Write '0x03' for enabling high speed SPI | 0x03 | 0x00 | Dummy data                              | 0x07 – Ultra High-Speed Mode<br>(100 MHz) |

Wait for 'CARD READY' from the module. This the first message that is read during wireless initialization.

**NOTE:** When an incorrect firmware is loaded onto the module, say chip version - 1.5 firmware is loaded on a 1.4 chipset, the **BOARD\_READY** message will be sent by the module but no **CARD\_READY** message will be sent to the host.

The Interrupt Status Register's (ISR) value is read before performing a frame read or frame write. Whenever the module sends data or a response to the host MCU, the register holds the value of 0x08. Whenever the host MCU wants to send or write a command frame to the module, the register holds the value of 0x00.

| MOSI Byte Explained                                                                           | MOSI | MISO | MISO Byte Explained                                      | Other         |  |

|-----------------------------------------------------------------------------------------------|------|------|----------------------------------------------------------|---------------|--|

| (Tx to Module)                                                                                |      |      | (Tx to Host MCU)                                         | Possibilities |  |

| Register Read                                                                                 | 0x41 | 0x00 | Dummy data                                               |               |  |

| RSI_SPI_INT_REG_ADDR Register<br>Address                                                      | 0x00 | 0x58 | Success token                                            | 0x52, 0x54    |  |

| Dummy data                                                                                    | 0x00 | 0x55 | Start token                                              |               |  |

| Dummy data                                                                                    | 0x00 | 0x08 | Module to send data to host                              |               |  |

| Pre-frame descriptor read                                                                     | 0x5C | 0x00 | Dummy data                                               |               |  |

| 8-bit mode                                                                                    | 0x00 | 0x58 | Success token                                            | 0x52, 0x54    |  |

| LSB of the number of bytes to be<br>read (Read first 4 bytes of the pre-<br>frame descriptor) | 0x04 | 0x58 | Success token                                            | 0x52, 0x54    |  |

| MSB of the number of bytes to be read                                                         | 0x00 | 0x58 | Success token                                            | 0x52, 0x54    |  |

| Dummy data                                                                                    | 0x00 | 0x58 | Success token for memory read                            | 0x52, 0x54    |  |

| Dummy data                                                                                    | 0x00 | 0x55 | Start token followed by four bytes                       |               |  |

| Dummy data                                                                                    | 0x00 | 0x14 | 0x14 - 0x04 = 16 bytes are to<br>be read from the module |               |  |

| Dummy data                                                                                    | 0x00 | 0x00 |                                                          |               |  |

| Dummy data                                                                                    | 0x00 | 0x04 |                                                          |               |  |

| Dummy data                                                                                    | 0x00 | 0x00 |                                                          |               |  |

| Frame Read                                                                                    | 0x5D | 0x00 | Dummy data                                               |               |  |

| 8-bit mode                                                                                    | 0x00 | 0x58 | Success token                                            | 0x52, 0x54    |  |

| LSB of the number of bytes to be read                                                         | 0x10 | 0x58 | Success token                                            | 0x52, 0x54    |  |

| MSB of the number of bytes to be read                                                         | 0x00 | 0x58 | Success token                                            | 0x52, 0x54    |  |

| Dummy data                                                                                    | 0x00 | 0x58 | Success token                                            | 0x52, 0x54    |  |

| Dummy data                                                                                    | 0x00 | 0x55 | Start token                                              |               |  |

| Dummy data                                                                                    | 0x00 | 0x00 | Payload length = 0                                       |               |  |

| Dummy data                                                                                    | 0x00 | 0x40 | 4 – Management Packet                                    |               |  |

| Dummy data                                                                                    | 0x00 | 0x89 | 0x89 – Command ID for CARD<br>READY                      |               |  |

| Dummy data                                                                                    | 0x00 | 0x00 |                                                          |               |  |

| Dummy data                                                                                    | 0x00 | 0x00 |                                                          |               |  |

| Dummy data | 0x00                  | 0x01                  |  |

|------------|-----------------------|-----------------------|--|

| Dummy data | Ten<br>dummy<br>bytes | Ten bytes of<br>zeros |  |

After the **'CARD READY'** message, every instruction or command is sent to the module via the 'Frame Write' operation, and the response from the module is read via the 'Frame Read' operation. Hence, these commands are termed Command frames.

Any command frame that is transferred between host and the module consists of **'Management frame'** (which constitutes the data payload length, management packet, and command ID) and **'data frame'**. Management frames are used to configure the Wi-Fi module to access Wi-Fi connectivity, TCP/IP stack, etc. Data frames are used to transfer the data.

| Data Payload length (x)<br>(Nibbles n3 n0 n1 - 12 b          |                                                                                                       |     |   |     |   |    |                                 |            |      |    |              |

|--------------------------------------------------------------|-------------------------------------------------------------------------------------------------------|-----|---|-----|---|----|---------------------------------|------------|------|----|--------------|

| Management frame (16 bytes) Length of data payload (x bytes) |                                                                                                       |     |   |     |   |    | ength of data payload (x bytes) |            |      |    |              |

| n0 n1 n2                                                     | n3 R                                                                                                  | R R | R | RR  | R | R  | R                               |            | R    | R  | Data payload |

| 0 1                                                          | 2 3                                                                                                   | 4 5 | 6 | 7 8 | 9 | 10 | 11                              | 12 13<br>Y | 3 14 | 15 |              |

| Management packet                                            | Command ID 0000 – when sent from host to module status of command - when sent from the module to host |     |   |     |   |    |                                 |            |      |    |              |

- The data payload length can be known from the nibbles n3 n0 n1 (with n3 being the most significant nibble) and should be retrieved in that order. For example, if the values of n0 n1 n2 n3 are 7 d 4 5 respectively, then the data payload length is (n3 n0 n1), i.e., 0x57d (1405 bytes).

- The 'n2' nibble determines the management packet.

- Every command frame has its own command ID.

4.5 Recommendations Based on Software Configurations

- The interrupt from the module is active high, and the host must be configured to interrupt in the level-triggered mode.

- The recommendation is to port the external interrupt GPIO Pin for interrupt status in the SPI HAL (Hardware Abstraction Layer).

- To configure a soft reset, the user needs to map the GPIO out pins of the host to the **'reset\_ext'** in the GPIO header of SiWN917.

- The user needs to send the reset sequence to the module in the function 'sl\_si91x\_host\_power\_cycle()'. For instance, the reset sequence for EFx32 host is already present in the definition at 'wiseconnect/components/si91x/platforms/efx32'.

The following are some of the possible reasons for SPI busy (error code - 0x0054):

- A command is sent before reading the complete response to the last command.

- A received packet is not completely read but the next send command is being sent.

- The packet intended to be sent was not sent completely.

- A glitch in SPI lines.

- High speed SPI is not supported.

While porting MCU HAL, ensure the data that is sent to MCU HAL in SPI Transfer function, 'sl\_si91x\_host\_spi\_transfer()', is placed in a buffer and its address is sent. Please refer to the 'sl\_si91x\_host\_spi\_transfer()' API description for more information.

## 5 Summary

SPI Communication behavior is dependent on Hardware and Software. Based on the above Hardware Design, and use case for Software Configuration, and analysis of ISSUE, a basic check can be done. HOST and SiWN917 modules should be properly interfaced to avoid data loss.

#### Disclaimer

Silicon Laboratories intends to provide customers with the latest, accurate, and in-depth documentation of all peripherals and modules available for system and software implementers using or intending to use the Silicon Laboratories products. Characterization data, available modules and peripherals, memory sizes and memory addresses refer to each specific device, and "Typical" parameters provided can and do vary in different applications. Application examples described herein are for illustrative purposes only. Silicon Laboratories reserves the right to make changes without further notice and limitation to product information, specifications, and descriptions herein, and does not give warranties as to the accuracy or completeness of the included information. Silicon Laboratories shall have no liability for the consequences of use of the information supplied herein. This document does not imply or express copyright licenses granted hereunder to design or fabricate any integrated circuits. The products must not be used within any Life Support System" is any product or system intended to support or sustain life and/or health, which, if it fails, can be reasonably expected to result in significant personal injury or death. Silicon Laboratories products are generally not intended for military applications. Silicon Laboratories products shall under no circumstances be used in weapons of mass destruction including (but not limited to) nuclear, biological or chemical weapons, or missiles capable of delivering such weapons.

#### **Trademark Information**

Silicon Laboratories Inc., Silicon Laboratories, Silicon Labs, SiLabs and the Silicon Labs logo, CMEMS®, EFM, EFM32, EFR, Energy Micro, Energy Micro logo and combinations thereof, "the world's most energy friendly microcontrollers", Ember®, EZLink®, EZMac®, EZRadio®, EZRadio®, DSPLL®, ISOmodem ®, Precision32®, ProSLIC®, SiPHY®, USBXpress® and others are trademarks or registered trademarks of Silicon Laboratories Inc. ARM, CORTEX, Cortex-M3 and THUMB are trademarks or registered trademarks of ARM Holdings. Keil is a registered trademark of ARM Limited. All other products or brand names mentioned herein are trademarks of their respective holders.

Silicon Laboratories Inc. 400 West Cesar Chavez Austin, TX 78701

http://www.silabs.com