# SiWx917 Family Reference Manual

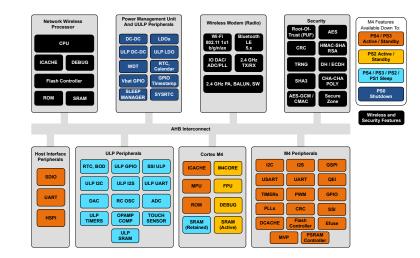

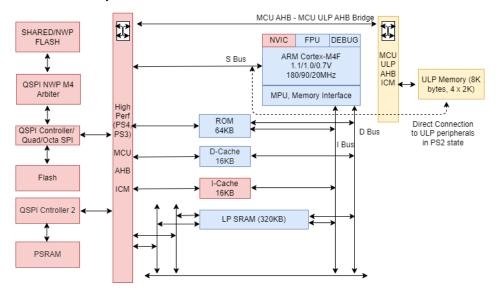

Silicon Labs SiWG917 SoC is our lowest power Wi-Fi 6 plus Bluetooth LE 5.4 SoC, ideal for ultra-low power IoT wireless devices using Wi-Fi<sup>®</sup>, Bluetooth, Matter, and IP networking for secure cloud connectivity. It is optimal for developing battery operated devices that need long battery life. SiWG917 SoC includes an ultra-low power Wi-Fi 6 plus Bluetooth Low Energy (LE) 5.4 wireless CPU subsystem, and an integrated micro-controller (MCU) application subsystem, security, peripherals and power management subsystem all in a single 7x7 mm QFN package. The wireless subsystem consists of a multi-threaded Network Wireless Processor (NWP) running up to 160 MHz, baseband digital signal processing, analog front end, 2.4 GHz RF transceiver and integrated power amplifier. The application subsystem consists of an ARM<sup>®</sup> Cortex<sup>®</sup>-M4 running up to 180 MHz, embedded SRAM, FLASH, ultra-low power sensor hub, and matrix vector processor. The ARM<sup>®</sup> Cortex<sup>®</sup>-M4 is dedicated for peripheral and application-related processing, while the NWP runs the wireless and networking stacks on independent threads, thus providing a fully integrated solution that is ready for a wide range of embedded wireless IoT applications.

SiWG917x applications include:

- Smart Home

- Security Cameras

- HVAC

- Smart Sensors

- Smart Appliances

- · Health and Fitness

- · Pet Trackers

- Smart Cities

- Smart Meters

- Industrial Wearables

- Smart Buildings

- Asset Tracking

- Smart hospitals

#### KEY FEATURES

- Wi-Fi 6 Single Band 2.4 GHz 20 MHz 1x1 stream IEEE 802.11 b/g/n/ax

- Bluetooth LE 5.4

- Single chip Matter Over Wi-Fi Solution

- ARM<sup>®</sup> Cortex<sup>®</sup> M4 Processor with FPU subsystem up to 180 MHz with rich set of Digital and Analog Peripherals.

- Wi-Fi 6 Benefits: TWT for improved efficiency and longer battery life, MU-MIMO/OFDMA for Higher Throughput, network capacity and low latency

- · Best in Class Device and Wireless Security

- WLAN Tx power up to +19.5 dBm with integrated PA

- Bluetooth LE Tx power up to +19 dBm with integrated PA

- WLAN Rx sensitivity as low as -97.5 dBm

- Wi-Fi Standby Associated mode current: 65 µA @ 1-second listen interval

- Embedded Flash option up to 8 MB/ optional external Flash up to 16 MB

- Embedded PSRAM option up to 8 MB/ optional external PSRAM option up to 16 MB

- Ultra-low power sensor hub peripherals

- Matrix Vector Processor (MVP)

- Embedded Wi-Fi, Bluetooth LE, Matter, and networking stacks supporting wireless coexistence

- Three software-configurable MCU application memory options for sharing the RAM between the wireless, system, and application (192/256/320 KB)

- Operating temperature: -40 °C to +85 °C

- Single or dual-supply operation:

- Single supply: 3.3 V

- · Dual supply: 3.3 V and 1.8 V

# **Table of Contents**

| 1. | Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 17                              |

|----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------|

|    | 1.1 Related Documentation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | .17                             |

| 2. | Feature List                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 18                              |

| 3. | System Processor                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | . 21                            |

|    | 3.1 Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                 |

|    | 3.2 FUnctional Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | .21                             |

|    | 3.3 Instruction Cache Controller       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | .21<br>.21<br>.22<br>.23        |

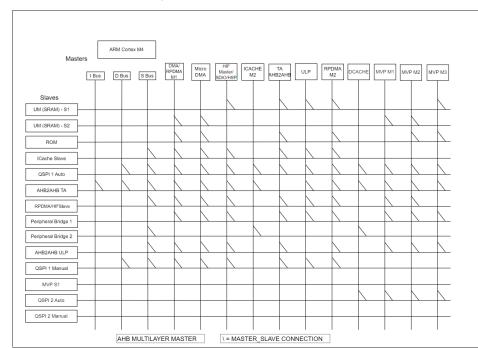

| 4. | MCU Bus Matrix                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | . 27                            |

|    | 4.1 General Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                 |

|    | 4.3 Functional Description       4.3.1 Overview       4.3.1 Overview       4.3.2 APB       4.3.2 APB       4.3.3 Primary and Secondary Details       4.3.4 Address Mapping       4.3.5 Register Summary       4.3.4 Address Compary       4.3.4 Address Mapping       4.3.4 Address Mapping <t< td=""><td>.27<br/>.27<br/>.28<br/>.30<br/>.32</td></t<> | .27<br>.27<br>.28<br>.30<br>.32 |

| 5. | Memory Architecture                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | . 33                            |

|    | 5.1 General Description       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       . <td>.33<br/>.33</td>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | .33<br>.33                      |

|    | 5.4 Unified Memory Architecture and Multiport       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       . <td< td=""><td>.34<br/>.34<br/>.34<br/>.34<br/>.34</td></td<>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | .34<br>.34<br>.34<br>.34<br>.34 |

|    | 5.5 Programming Sequence                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | .35                             |

|    | 5.6 Register Summary.       5.7 Register Description         5.7 Register Description       5.7.1 ENABLE_TRAP_REG         5.7.1 ENABLE_TRAP_REG       5.7.2 TRAP_DETECTED_REG_LP_SRAM_192K                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | .37<br>.37                      |

|    | 5.7.3 TRAP_STATUS_LPSRAM_192K                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                 |

|    | 5.7.4 TRAP_STATUS_LP_SRAM_64K0    |   | .38  |

|----|-----------------------------------|---|------|

|    | 5.7.5 TRAP_CLEAR_LP_SRAM_192K     |   | .38  |

|    | 5.7.6 TRAP_CLEAR_LP_SRAM_64K0     |   | .38  |

|    | 5.7.7 TRAP_DETECTED_LP_SRAM_64K0. |   | .39  |

|    | 5.7.8 TRAP_STATUS_LP_SRAM_64K1    |   | .39  |

|    | 5.7.9 TRAP_CLEAR_LP_SRAM_64K1     |   |      |

|    | 5.7.10 TRAP_DETECTED_LP_SRAM_64K1 |   |      |

|    |                                   |   |      |

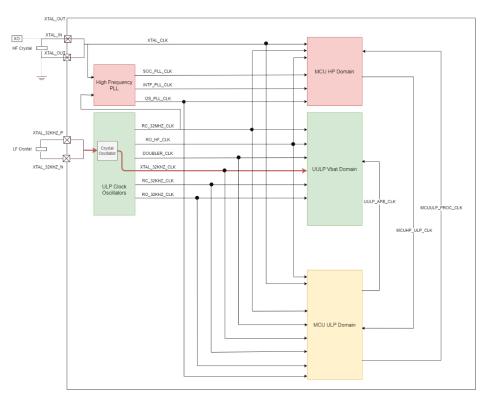

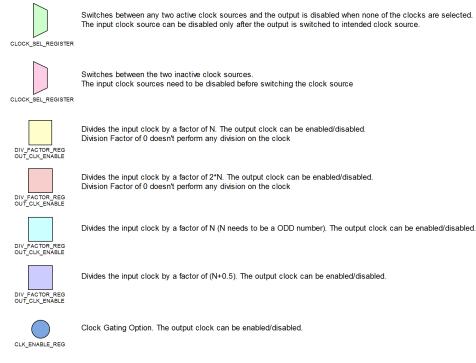

| 6. | Clock Architecture                | • | . 41 |

|    | 6.1 General Description           |   | .41  |

|    | 6.2 Features                      |   | .41  |

|    | 6.3 Functional Description        |   | .42  |

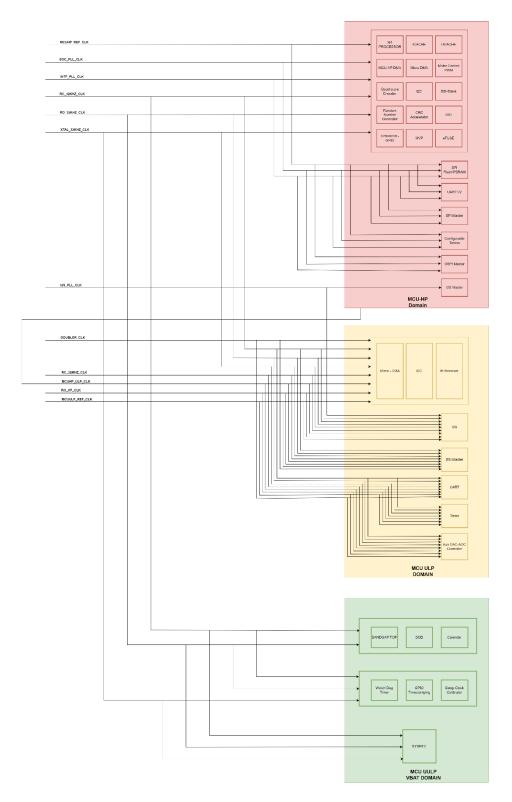

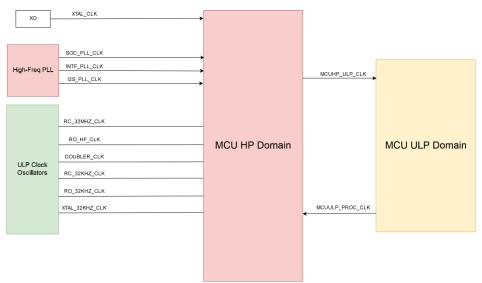

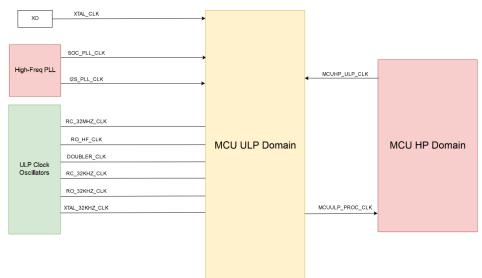

|    | 6.3.1 Overview                    |   |      |

|    |                                   |   |      |

|    | 6.4 HF Crystal Clock              |   |      |

|    | 6.5 Naming Convention             |   |      |

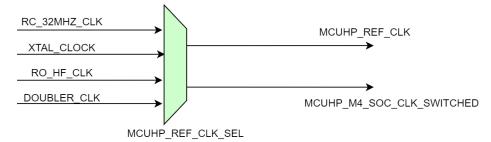

|    | 6.6 Reference Clock               |   |      |

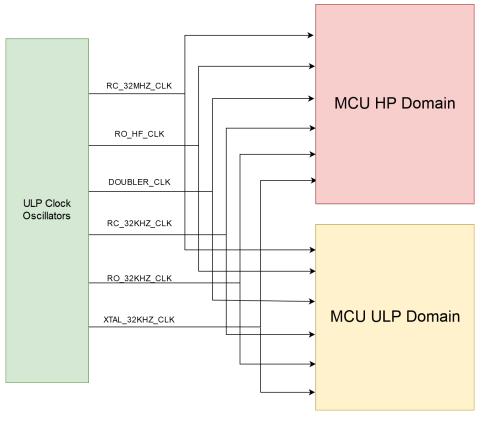

|    | 6.6.1 MCU HP                      |   | .44  |

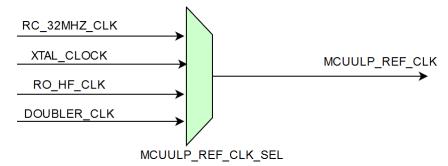

|    | 6.6.2 MCU ULP                     |   | .45  |

|    | 6.7 Clocking Schemes.             |   | .45  |

|    | 6.8 Register Summary.             |   | .45  |

|    | 6.9 Register Description          |   |      |

|    | 6.9.1 MCU_REF_CLK_CONFIG          |   |      |

|    | 6.10 Clock Distribution.          |   |      |

|    |                                   |   |      |

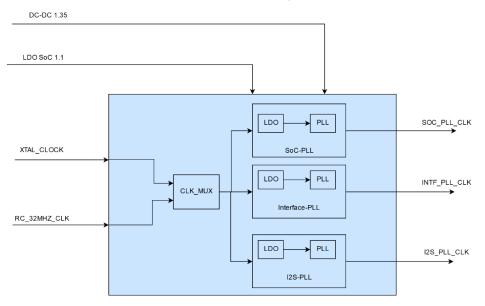

|    | 6.11 High-Frequency PLL           |   |      |

|    | 6.11.1 General Description        |   |      |

|    | 6.11.2 Features                   |   |      |

|    | 6.11.3 Functional Description     |   |      |

|    | 6.11.4 Input Reference Clock      |   |      |

|    | 6.11.5 SoC-PLL                    |   |      |

|    | 6.11.6 Interface-PLL              |   |      |

|    | 6.11.7 I2S-PLL                    |   |      |

|    | 6.11.8 PLL Programming Baud Rate  |   |      |

|    | 6.11.9 Register Summary           |   | .53  |

|    | 6.11.10 Register Description      |   | .54  |

|    | 6.12 MCU HP Clock Architecture    |   | .59  |

|    | 6.12.1 General Description        |   | .59  |

|    | 6.12.2 Features                   |   | .59  |

|    | 6.12.3 Functional Description     |   | .60  |

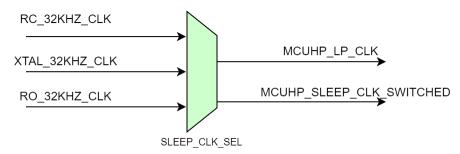

|    | 6.12.4 Low-Power Clock            |   |      |

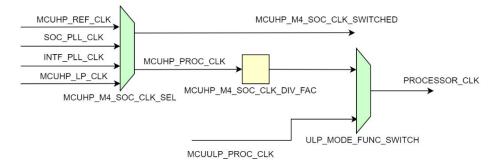

|    | 6.12.5 Processor.                 |   |      |

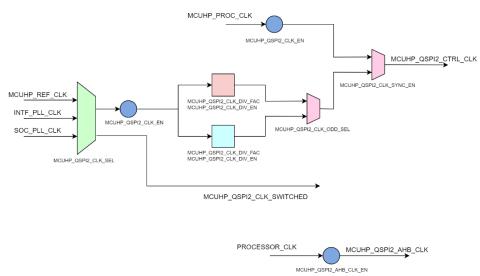

|    | 6.12.6 SPI Flash Controller       |   |      |

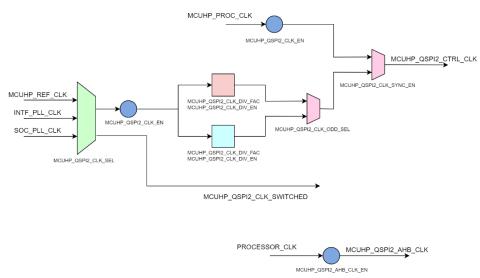

|    | 6.12.7 SPI PSRAM Controller       |   | -    |

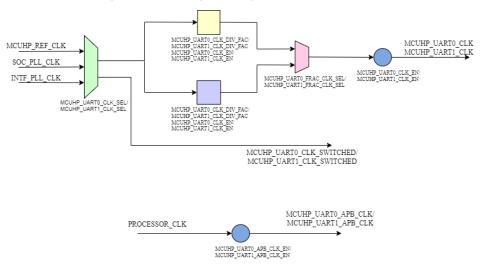

|    | 6.12.8 UARTO/UART1                |   |      |

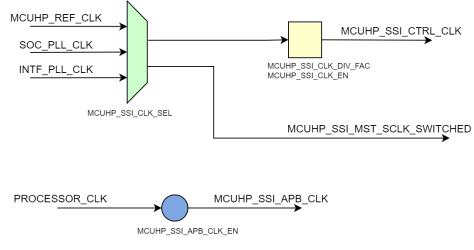

|    | 6.12.9 SPI / SSI Primary          |   |      |

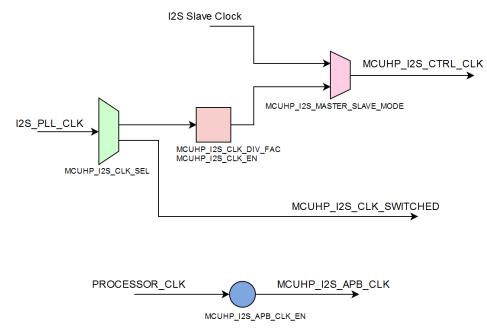

|    | $6.12.10 \ I^2S \ Controller$     |   |      |

|    |                                   |   | .00  |

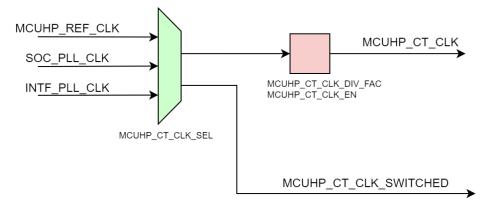

| 6.12.11 Configurable Timers              | 67  |

|------------------------------------------|-----|

| 6.12.12 MVP                              |     |

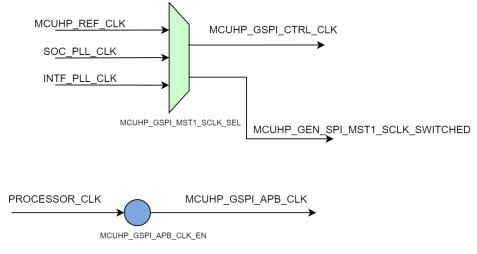

| 6.12.13 Generic SPI Primary              |     |

| 6.12.14 MCU-ULP SoC Clock                |     |

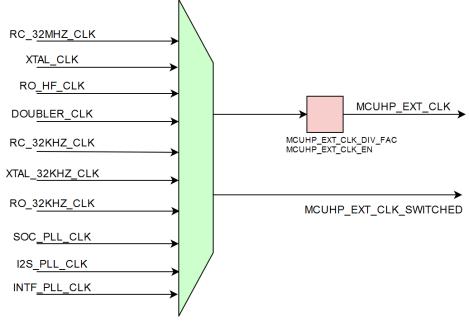

| 6.12.15 External Clock                   |     |

| 6.12.16 Static Clock Gated Domains       | 70  |

| 6.12.17 Register Summary                 | 71  |

| 6.12.18 Register Description             | 72  |

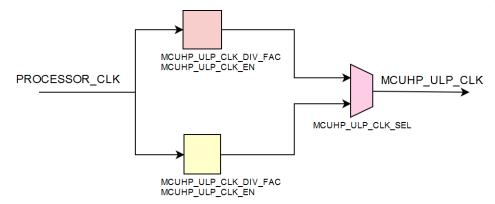

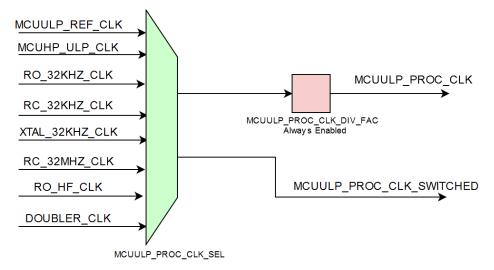

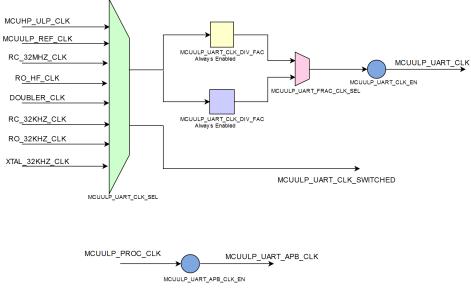

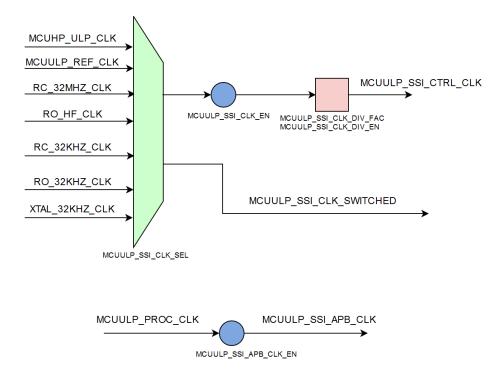

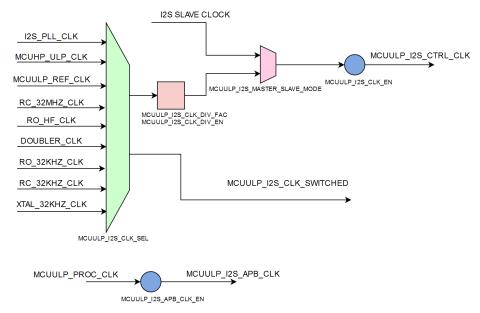

| 6.13 MCU ULP Clock Architecture          | 118 |

| 6.13.1 General Description               |     |

| 6.13.2 Features                          |     |

| 6.13.3 Functional Description            |     |

| 6.13.4 AHB Interface Clock               |     |

| 6.13.5 UART                              |     |

| 6.13.6 SPI / SSI Primary                 |     |

| $6.13.7 I^2S$ Controller                 |     |

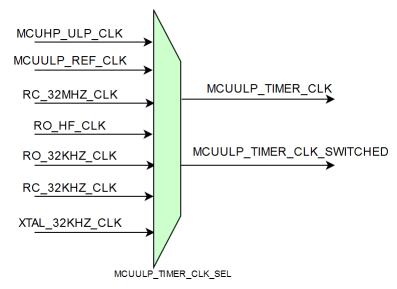

| 6.13.8 Timer                             |     |

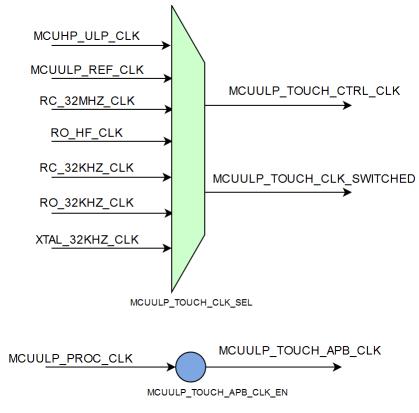

| 6.13.9 Touch Sensor                      |     |

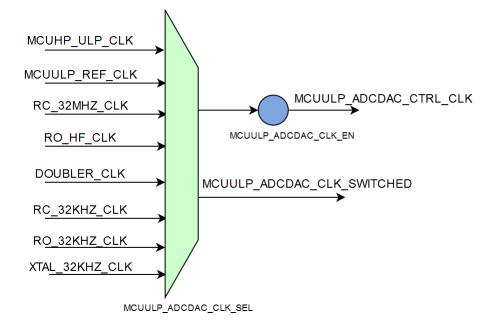

| 6.13.10 Aux-ADC/DAC Controller           |     |

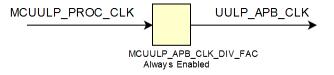

| 6.13.11 UULP APB Clock                   |     |

| 6.13.12 Static Clock Gated Domains       |     |

| 6.13.13 Register Summary                 |     |

| 6.13.14 Register Description             |     |

|                                          |     |

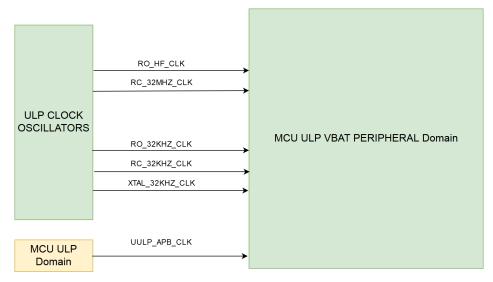

| 6.14 MCU ULP VBAT Clock Architecture     |     |

| 6.14.1 General Description               |     |

| 6.14.2 Features                          |     |

| 6.14.3 Functional Description            |     |

| 6.14.4 Register Summary                  |     |

| 6.14.5 Register Description              |     |

| 6.15 ULP Clock Oscillators               |     |

| 6.15.1 General Description               |     |

| 6.15.2 Features                          |     |

| 6.15.3 Functional Description            | 153 |

| 6.15.4 Register Summary                  | 153 |

| 6.15.5 Register Description              | 154 |

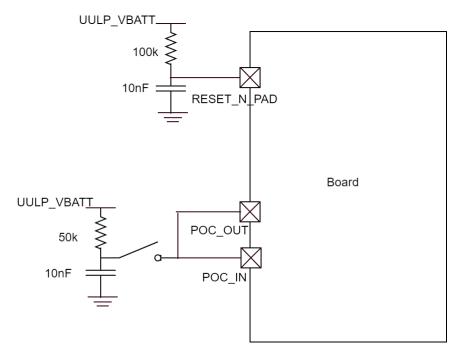

| 7. Resets                                | 155 |

| 7.1 General Description                  |     |

|                                          |     |

| 7.2 Features                             |     |

| 7.3 Functional Description               |     |

| 7.3.1 RESET_N_PAD                        |     |

| 7.3.2 POC_IN                             |     |

| 7.3.3 Black Out Monitor                  |     |

| 7.3.4 WatchDog Reset                     | 156 |

| 7.4 Reset request from host or Processor | 156 |

| 7.5 Register Summary                     | 156 |

|    | 7.6 Register Description <th></th>                                              |   |

|----|---------------------------------------------------------------------------------|---|

| 8. | Interrupts                                                                      | 7 |

|    | 8.1 General Description                                                         | 7 |

|    | 8.2 Features                                                                    | 7 |

|    | 8.3 Functional Description                                                      | 7 |

|    | 8.3.1 Flexible Exception and Interrupt Management                               |   |

|    | 8.3.2 Nested Exception/Interrupt Support                                        |   |

|    | 8.3.3 Vectored Exception/Interrupt Entry                                        |   |

|    | 8.3.5 Vector Table                                                              |   |

|    | 8.3.6 Vectored Interrupt Table (VIT)                                            | 8 |

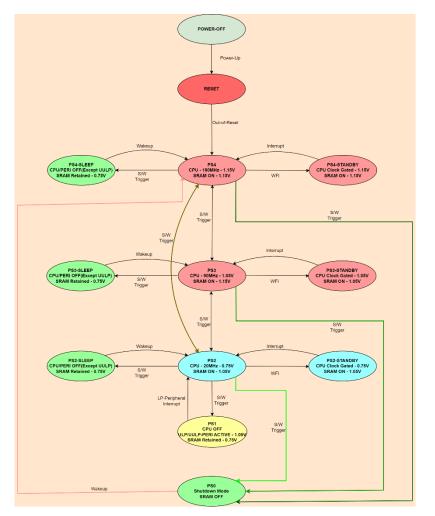

| 9. | Power Architecture                                                              | 4 |

|    | 9.1 General Description                                                         | 4 |

|    | 9.2 Features                                                                    | 4 |

|    | 9.3 Functional Description                                                      | 5 |

|    | 9.3.1 Power Domains                                                             | 5 |

|    | 9.3.2 Programming Sequence                                                      |   |

|    | 9.4 Voltage Domains                                                             |   |

|    | 9.5 Power States                                                                |   |

|    | 9.5.1 PS4                                                                       |   |

|    | 9.5.3 PS2                                                                       |   |

|    | 9.5.4 PS1                                                                       | 2 |

|    | 9.5.5 STANDBY                                                                   |   |

|    | 9.5.6 SLEEP                                                                     |   |

|    | 9.5.8 Programming Sequence for Transitions                                      |   |

|    | 9.6 Blocks Availability in Different Power States                               | 7 |

|    | 9.7 Memory Retention in Sleep / Shutdown states                                 | 8 |

|    | 9.8 Wakeup Sources                                                              | 9 |

|    | 9.9 Register Summary                                                            | 0 |

|    | 9.9.1 High-Performance Power Domains                                            |   |

|    | 9.9.2 Low-Power Domains       19         9.9.3 Ultra Low-Power Domains       19 |   |

|    | 9.9.4 Analog Domains                                                            |   |

|    | 9.9.5 SLEEP FSM                                                                 |   |

|    | 9.9.6 ULP Configuration                                                         |   |

|    | 9.9.7 MCU Retention                                                             |   |

|    | 9.10 Register Description                                                       |   |

|    | 9.10.1 M4SS_BYPASS_PWRCTRL_REG1                                                 |   |

|    | 9.10.3 M4SS_PWRCTRL_SET_REG                                                     |   |

| 9.10.4 N | /4SS_PWRCTRL_CLEAR_REG              | . 198 |

|----------|-------------------------------------|-------|

| 9.10.5 N | /4SS_PLL_PWRCTRL_REG                | . 199 |

| 9.10.6 N | //4_SRAM_PWRCTRL_SET_REG1           | . 199 |

| 9.10.7 N | //4_SRAM_PWRCTRL_CLEAR_REG1         | 200   |

| 9.10.8 N | //4_SRAM_PWRCTRL_SET_REG2           | . 200 |

| 9.10.9 N | //4_SRAM_PWRCTRL_CLEAR_REG2         | 201   |

| 9.10.10  | M4_SRAM_PWRCTRL_SET_REG3            | .202  |

| 9.10.11  | M4_SRAM_PWRCTRL_CLEAR_REG3          | .203  |

| 9.10.12  | M4_SRAM_PWRCTRL_SET_REG4            | .203  |

| 9.10.13  | M4_SRAM_PWRCTRL_CLEAR_REG4          | .203  |

| 9.10.14  | MCU_FSM_CTRL_BYPASS                 | . 204 |

| 9.10.15  | MCU_PMU_LDO_CTRL_SET                | 205   |

|          | MCU_PMU_LDO_CTRL_CLEAR              | 206   |

|          | ULPSS_PWRCTRL_SET_REG               | . 207 |

|          | ULPSS_PWRCTRL_CLEAR_REG             | . 208 |

|          | ULPSS RAM PWRCTRL REG1 SET          | 208   |

|          | ULPSS_RAM_PWRCTRL_REG1_CLEAR        | .209  |

|          | ULPSS_RAM_PWRCTRL_REG2_SET          | 209   |

|          | ULPSS_RAM_PWRCTRL_REG2_CLEAR        | .209  |

|          | ULPSS_RAM_PWRCTRL_REG3_SET          | 210   |

|          | ULPSS_RAM_PWRCTRL_REG3_CLEAR        | .210  |

|          | UULP_PWRCTRL_SET                    | 211   |

|          | UULP_PWRCTRL_CLEAR                  | 213   |

|          | MCUAON_IPMU_RESET_CTRL              | 214   |

|          | MCUAON_SHELF_MODE.                  | 215   |

|          | MCUAON GEN CTRLS                    | .216  |

|          | MCUAON PDO CTRLS                    | .217  |

|          | MCUAON_WDT_CHIP_RST                 | . 217 |

|          | MCUAON_KHZ_CLK_SEL_POR_RESET_STATUS | . 218 |

|          | MCU FSM SLEEP CTRLS AND WAKEUP MODE | 220   |

|          | MCU_FSM_PERI_CONFIG_REG             | .222  |

|          | MCU_FSM_POWER_CTRL_AND_DELAY        |       |

|          | GPIO WAKEUP REGISTER.               |       |

|          | MCU_FSM_DEEP_SLEEP_DURATION_LSB_REG |       |

|          | MCU_FSM_XTAL_AND_PMU_GOOD_COUNT_REG |       |

|          | MCU FSM CLKS REG                    |       |

|          | MCU_FSM_REF_CLK_REG                 |       |

|          | MCU_FSM_CLK_ENS_AND_FIRST_BOOTUP    |       |

|          | MCU_FSM_CRTL_PDM_AND_ENABLES        |       |

|          | MCU_FSM_CKTL_FDM_AND_ENABLES        |       |

|          | MCU_GPIO_TIMESTAMPING_CONFIG        |       |

|          |                                     |       |

|          | MCU_SLEEPHOLD_REQ                   |       |

|          | MCU_FSM_WAKEUP_STATUS_REG           |       |

|          | MCU_FSM_WAKEUP_STATUS_CLEAR         |       |

|          | MCU_FSM_PMU_STATUS_REG              |       |

|          | MCU_FSM_PMUX_CTRLS_RET              |       |

|          | MCU_FSM_TOGGLE_COUNT                |       |

| 9.10.51  | M4SS_TASS_CTRL_SET_REG.             | . 238 |

| 9.10.52 M4SS_TASS_CTRL_CLEAR_REG                    | 238   |

|-----------------------------------------------------|-------|

| 9.10.53 M4_ULP_MODE_CONFIG                          |       |

| 9.10.54 ULPSS_BYPASS_PWRCTRL_REG                    |       |

| 9.10.55 Analog_Power_Control                        |       |

| 9.10.56 MCURET_QSPI_WR_OP_DIS                       |       |

| 9.10.57 MCURET_BOOTSTATUS                           | 243   |

| 9.10.58 CHIP_CONFIG_MCU_READ                        | 244   |

| 9.10.59 MCUAON_CTRL_REG4                            | 246   |

| 9.10.60 NPSS_GPIO_0_CTRLS                           | 248   |

| 9.10.61 NPSS_GPIO_1_CTRLS                           | 249   |

| 9.10.62 NPSS_GPIO_2_CTRLS                           | 250   |

| 9.10.63 NPSS_GPIO_3_CTRLS                           | 251   |

| 9.10.64 NPSS_GPIO_4_CTRLS                           | 252   |

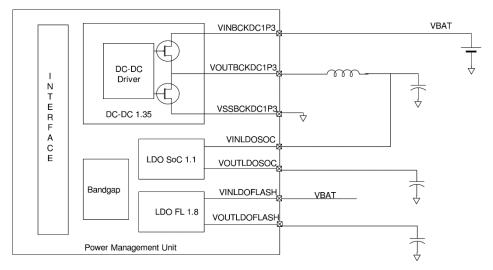

| 10. Power Management Unit                           | 253   |

| 10.1 Features                                       | 253   |

| 10.2 Functional Description                         | . 253 |

| 10.2.1 Block Diagram                                |       |

| 10.2.2 Modes of Operation                           |       |

| 10.3 Register Summary                               |       |

| 10.4 Register Description                           | 254   |

| 10.4.1 PMU_IP3_CTRL_REG                             |       |

| 10.4.2 PMU_LDOSOC_REG.                              |       |

|                                                     |       |

| 10.5 PMU Good Time                                  |       |

| 10.5.1 Direct Battery Connected PMU Good Time       |       |

|                                                     |       |

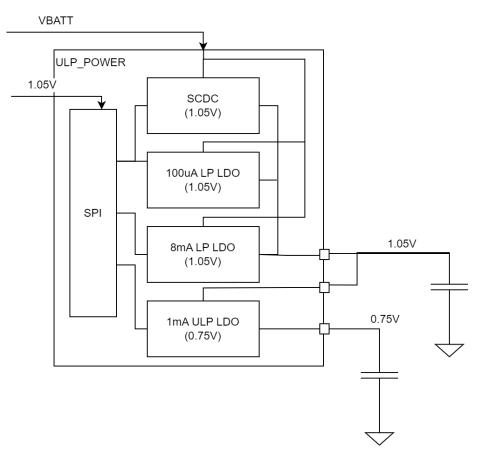

| 11. ULP Regulators                                  | . 257 |

| 11.1 General Description                            | 257   |

| 11.2 Features                                       | 257   |

| 11.3 Functional Description                         | 258   |

| 11.3.1 Block Diagram                                |       |

| 11.4 Register Summary                               |       |

|                                                     |       |

| 11.5 Register Description.                          |       |

| 11.5.1 SCDC_CTRL_REG_0                              |       |

| 11.5.2 BG_SCDC_PROG_REG_1                           |       |

| 11.5.3 BG_SCDC_PROG_REG_2                           |       |

| 11.5.4 BG_LDO_REG                                   | . 201 |

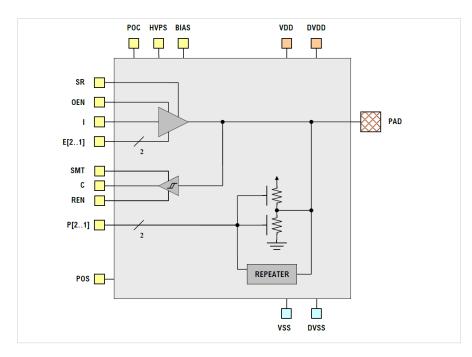

| 12. Pad Configurations                              |       |

| 12.1 General Description                            | 262   |

| 12.2 Features                                       | 262   |

| 12.3 Functional Description                         | . 263 |

| 12.3.1 PAD Description                              | 264   |

| 12.3.2 Programming Sequence                         | 266   |

| 12.3.3 PAD Configuration and GPIO Mode Reset Values | .269  |

| 12.4 Register Summary       12.4.1 PAD Selection Registers         12.4.1 PAD Selection Registers       12.4.2 MCU HP GPIO PAD Configuration Registers         12.4.2 MCU ULP GPIO PAD Configuration Registers       12.4.3 MCU ULP GPIO PAD Configuration Registers         12.4.4 MCU UULP Vbat GPIO PAD Configuration Registers       12.4.4 MCU UULP Vbat GPIO PAD Configuration Registers                                                  | 270<br>271<br>271                                     |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------|

| 12.5 Register Description.       12.5.1 MCUHP_PAD_SELECTION         12.5.2 MCUHP_PAD_SELECTION_1.       12.5.2 MCUHP_PAD_SELECTION_1.         12.5.3 MEM_GPIO_ACCESS_CTRL_SET       12.5.4 MEM_GPIO_ACCESS_CTRL_CLEAR         12.5.4 MEM_GPIO_ACCESS_CTRL_CLEAR       12.5.5 PAD_CONFIG_REG_n         12.5.6 ULP_PAD_CONFIG_REG0.       12.5.7 ULP_PAD_CONFIG_REG1.         12.5.8 ULP_PAD_CONFIG_REG2.       12.5.9 UULP_VBAT_GPIOn_CONFIG_REG | 271<br>272<br>272<br>272<br>.273<br>274<br>276<br>277 |

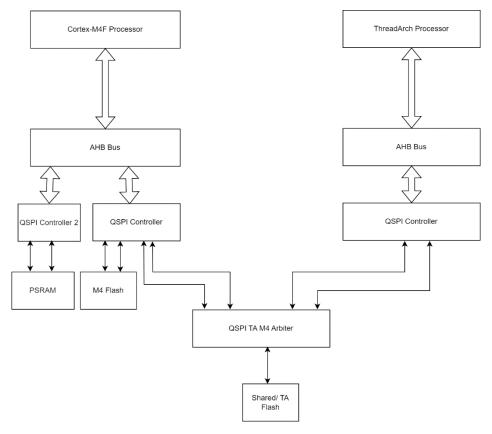

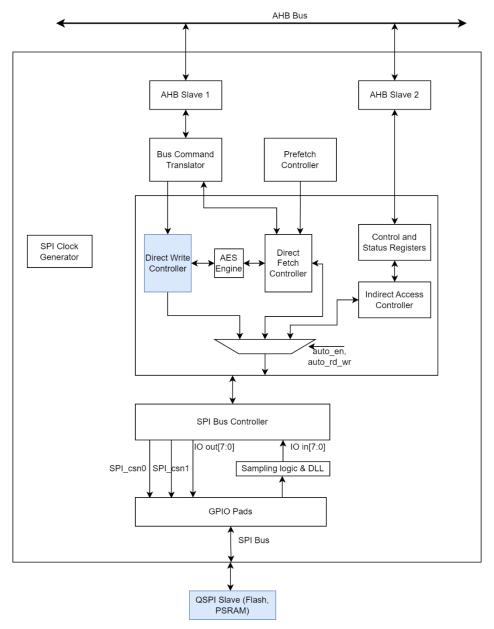

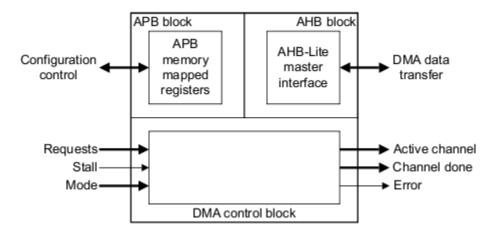

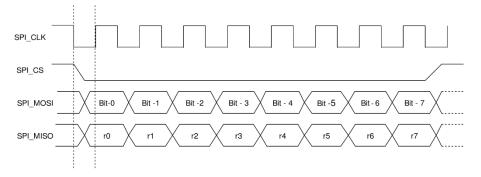

| 13. SPI Flash/PSRAM Controller                                                                                                                                                                                                                                                                                                                                                                                                                  | .278                                                  |

| 13.1 General Description                                                                                                                                                                                                                                                                                                                                                                                                                        | 278                                                   |

| 13.2 Features                                                                                                                                                                                                                                                                                                                                                                                                                                   | 278                                                   |

| 13.3 Functional Description                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                       |

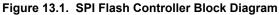

| 14. GPDMA                                                                                                                                                                                                                                                                                                                                                                                                                                       | 295                                                   |

| 14.1 General Description                                                                                                                                                                                                                                                                                                                                                                                                                        | 295                                                   |

| 14.2 Features                                                                                                                                                                                                                                                                                                                                                                                                                                   | 295                                                   |

| 14.3 Functional Description                                                                                                                                                                                                                                                                                                                                                                                                                     | 296                                                   |

| 14.4 Programming Sequence                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                       |

| 14.4.1 Interrupt Configurations of GPDMA                                                                                                                                                                                                                                                                                                                                                                                                        |                                                       |

| 14.4.2 FIGURE-Configuration                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                       |

| 14.5 Register Summary                                                                                                                                                                                                                                                                                                                                                                                                                           | .299                                                  |

| 14.6 Register Description.                                                                                                                                                                                                                                                                                                                                                                                                                      | 300                                                   |

| 14.6.1 INTERRUPT_REG                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                       |

| 14.6.2 INTERRUPT_MASK_REG                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                       |

| 14.6.4 DMA CHNL ENABLE REG                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                       |

| 14.6.5 DMA_CHNL_SQUASH_REG                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                       |

| 14.6.6 DMA_CHNL_LOCK_REG                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                       |

| 14.6.7 LINK_LIST_PTR_REG_CHNL_n                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                       |

| 14.6.9 DEST_ADDR_REG_CHNL_n                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                       |

| 14.6.10 CHANNEL_CTRL_REG_CHNL_n                                                                                                                                                                                                                                                                                                                                                                                                                 | . 306                                                 |

| 14.6.11 MISC_CHANNEL_CTRL_REG_CHNL_n                                                                                                                                                                                                                                                                                                                                                                                                            |                                                       |

| 14.6.12 FIFO_CONFIG_REG_CHNL_n                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                       |

| 14.6.13 PRIORITY_LEVEL_REG_CHNL_n                                                                                                                                                                                                                                                                                                                                                                                                               | 308                                                   |

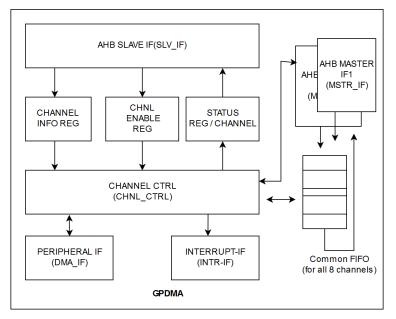

| 15. UDMA                                                                                                                                                                                                                                                                                                                                                                                                                                        | 309                                                   |

| 15.1 General Description            | 309  |

|-------------------------------------|------|

| 15.2 Features                       | 309  |

| 15.3 Functional Description         | 310  |

| 15.4 Programming Sequence           | .311 |

| 15.5 Register Summary               | .312 |

| 15.6 Register Description.          | 313  |

| 15.6.1 DMA_STATUS                   |      |

| 15.6.2 DMA_CFG                      |      |

| 15.6.3 CTRL_BASE_PTR                |      |

| 15.6.5 DMA_WAITONREQUEST_STATUS     |      |

| 15.6.6 CHNL_SW_REQUEST              | .314 |

| 15.6.7 CHNL_USEBURST_SET            |      |

| 15.6.8 CHNL_USEBURST_CLR            |      |

| 15.6.10 CHNL REQ MASK CLR           |      |

| 15.6.11 CHNL_ENABLE_SET             |      |

| 15.6.12 CHNL_ENABLE_CLR             |      |

| 15.6.13 CHNL_PRI_ALT_SET            |      |

| 15.6.14 CHNL_PRI_ALT_CLR            |      |

| 15.6.16 CHNL_PRIORITY_CLR           |      |

| 15.6.17 ERR_CLR                     |      |

| 15.6.18 SKIP_DESC_FETCH             |      |

| 15.6.19 UDMA_DONE_STATUS            |      |

| 15.6.21 UDMA PERIPHERAL SEL CHn REG |      |

| 15.6.22 UDMA_CONFIG_CTRL            |      |

| 16. MCU Peripherals                 | 324  |

| 16.1 HSPI Secondary                 | 324  |

| 16.1.1 General Description          |      |

| 16.1.2 Features                     |      |

| 16.1.3 Functional Description       |      |

| 16.1.5 Register Description         |      |

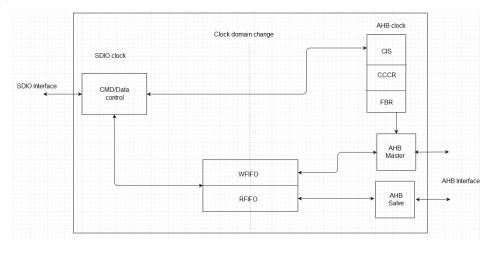

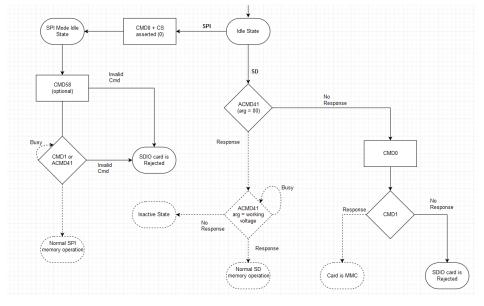

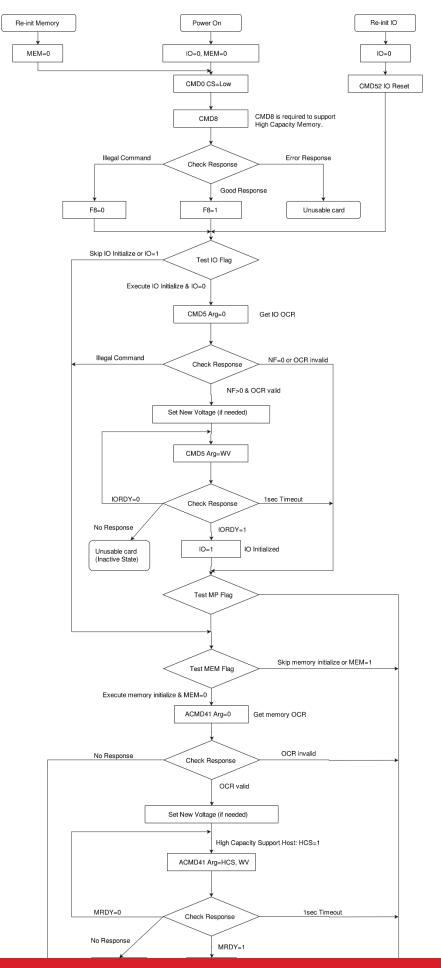

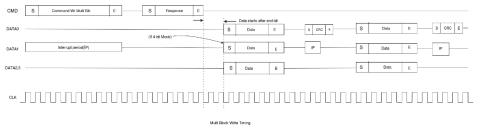

| 16.2 SDIO Secondary                 |      |

| 16.2.1 General Description          |      |

| 16.2.2 Features                     |      |

| 16.2.3 Functional Description       |      |

| 16.2.4 Register Summary             |      |

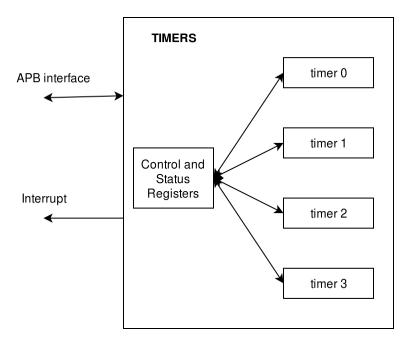

| 16.3 Configurable Timers.           |      |

| 16.3.1 General Description          |      |

| 16.3.2 Features                     |      |

| 16.3.3 Functional Description       | 374  |

| 16.3.4 Register Summary                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 378<br>380                        |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------|

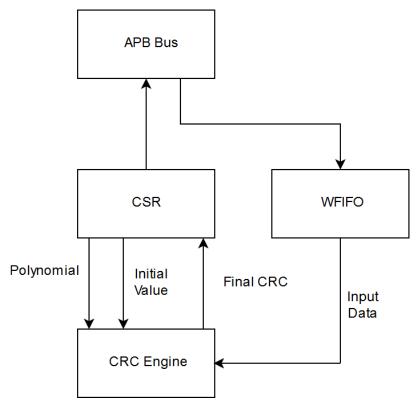

| 16.4 CRC Accelerator   16.4.1 General Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 409                               |

| 16.4.2 Features                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 410                               |

| 16.4.5 Register Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | .412                              |

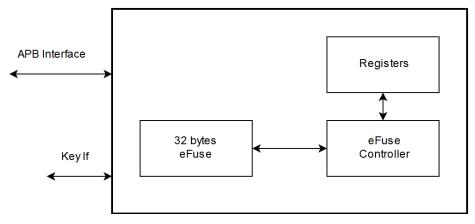

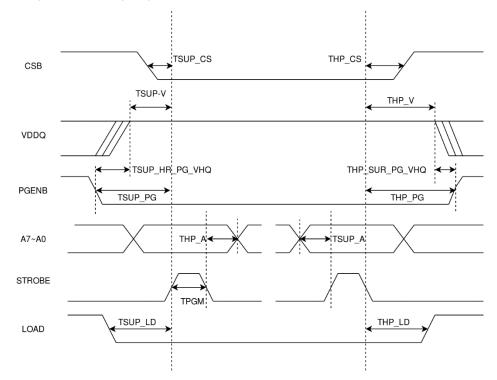

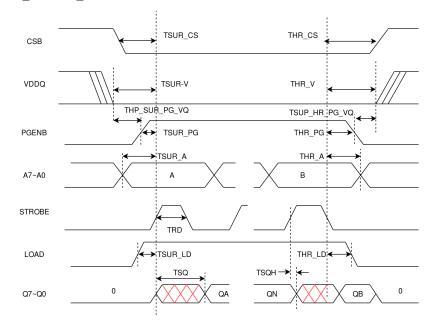

| 16.5 eFuse Controller       16.5.1 General Description         16.5.2 Features       16.5.3 Functional Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | .417<br>.417                      |

| 16.5.4 Register Summary    16.5.5 Register Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                   |

| 16.6 Enhanced GPIO (EGPIO)       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .                          | 427                               |

| 16.6.3 Functional Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 430                               |

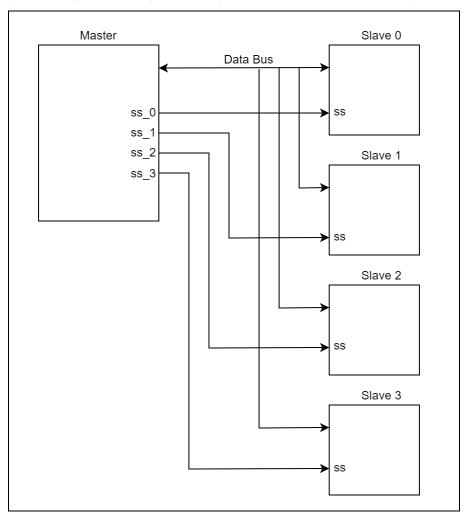

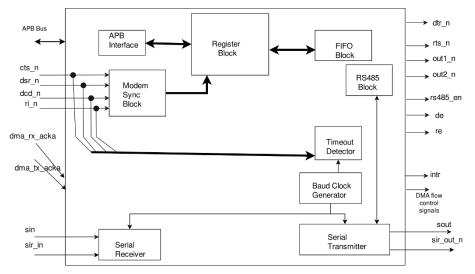

| 16.7 Generic SPI Primary       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1 </td <td>435<br/>.436</td> | 435<br>.436                       |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 438                               |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 447<br>447                        |

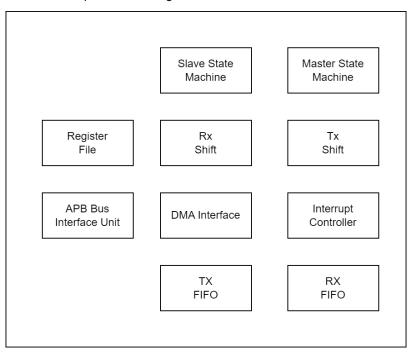

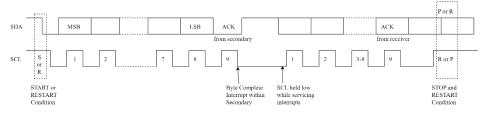

| 16.9 I2C Primary and Secondary                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 448<br>.448<br>449<br>.450<br>452 |

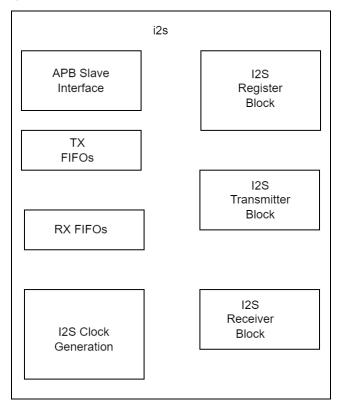

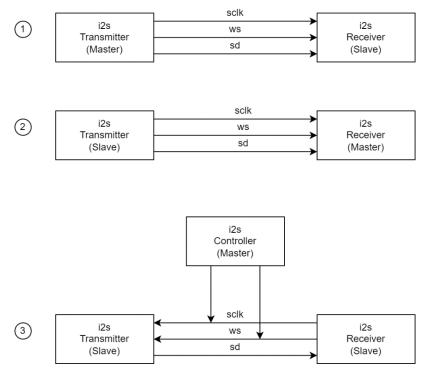

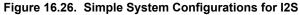

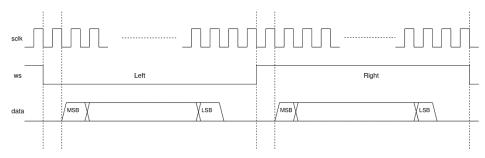

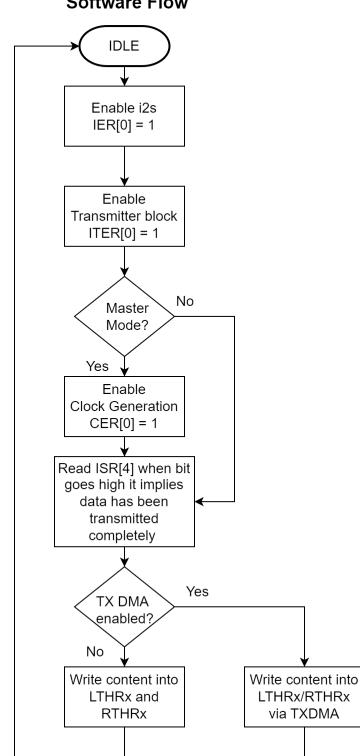

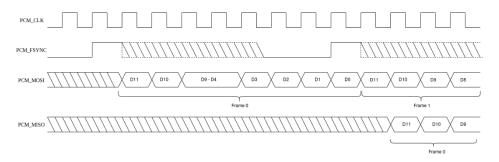

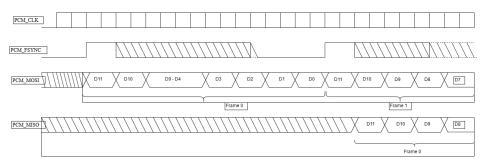

| 16.10       I2S/PCM Primary and Secondary         16.10.1       General Description         16.10.2       Features         16.10.3       Functional Description         16.10.4       Programming Sequence of I2S                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 484<br>484<br>485                 |

| 16.10.4       Programming Sequence of 125                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 493                               |

| 16.10.7   | Register Description                            | 495   |

|-----------|-------------------------------------------------|-------|

| 16.11 MC  | CU Configuration Registers                      | 507   |

|           | General Description                             |       |

|           | Features                                        |       |

|           | Functional Description                          |       |

|           | Register Summary                                |       |

|           | Register Description                            |       |

|           | MCU HP Peripheral Interrupt Handling            |       |

|           | Programming Sequence for P2P Interrupt Handling |       |

|           |                                                 |       |

|           |                                                 |       |

|           |                                                 |       |

|           |                                                 |       |

|           |                                                 |       |

|           |                                                 |       |

|           | Register Summary                                |       |

|           | Register Description                            |       |

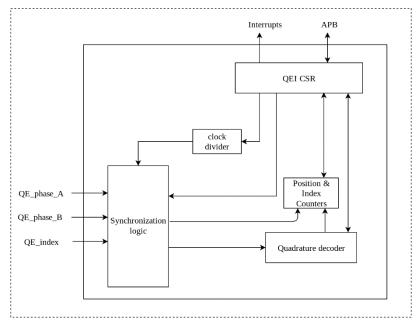

|           | adrature Encoder                                |       |

|           | General Description                             |       |

| 16.13.2   | Features                                        | 574   |

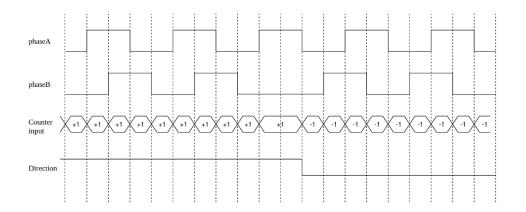

| 16.13.3   | Functional Description                          | .575  |

| 16.13.4   | Register Summary                                | 577   |

| 16.13.5   | Register Description                            | 577   |

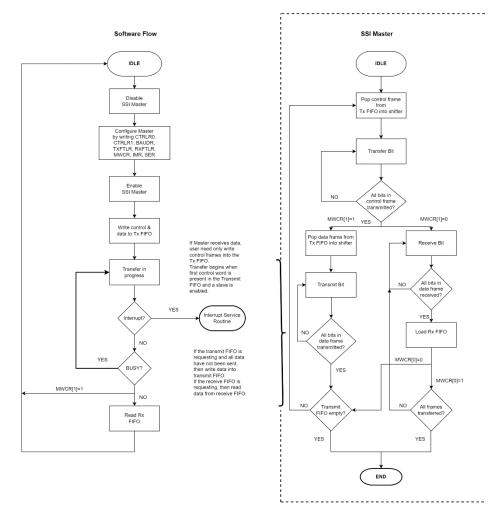

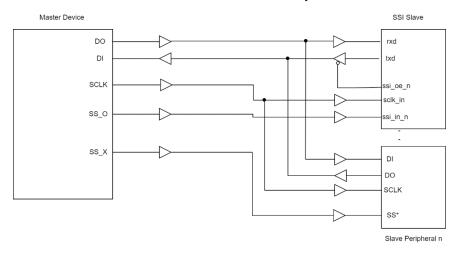

| 16.14 SSI | Primary                                         | . 589 |

|           | General Description                             |       |

|           | Features                                        |       |

|           | Functional Description                          |       |

|           | SSI Interrupts                                  |       |

|           | Programming Sequence                            |       |

|           | Register Summary                                |       |

|           | Register Description                            | 596   |

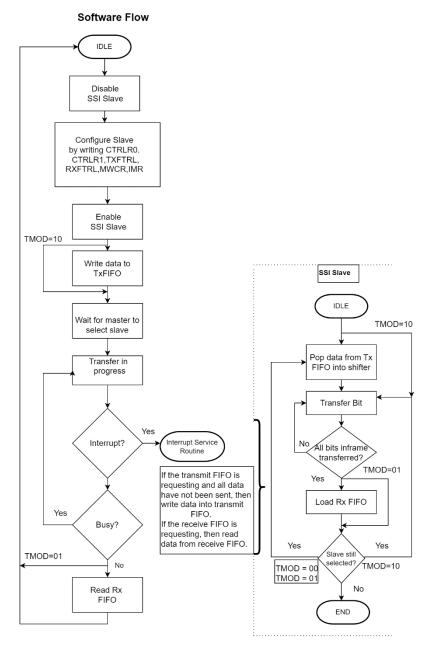

|           | Secondary                                       |       |

|           |                                                 |       |

|           |                                                 |       |

|           |                                                 |       |

|           |                                                 |       |

|           | Programming Sequence for Data Transfer          |       |

|           | Register Summary                                |       |

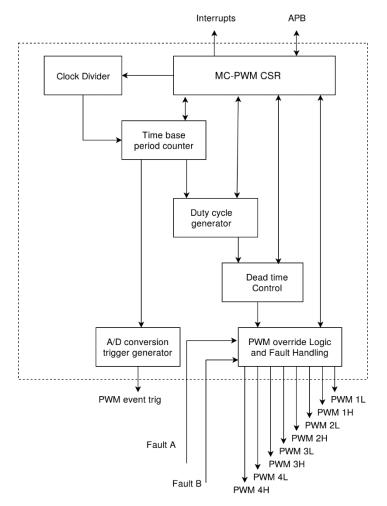

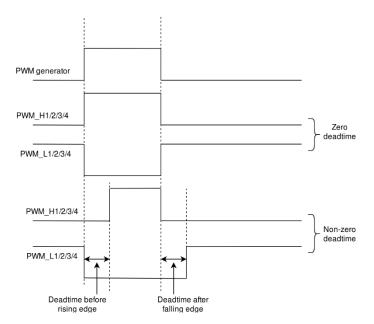

|           | Register Description                            |       |